# High-Throughput Modular Multiplication and Exponentiation Algorithms Using Multibit-Scan–Multibit-Shift Technique

Abdalhossein Rezai and Parviz Keshavarzi

Abstract-Modular exponentiation with a large modulus and exponent is a fundamental operation in many public-key cryptosystems. This operation is usually accomplished by repeating modular multiplications. Montgomery modular multiplication has been widely used to relax the quotient determination. The carry-save adder has been employed to reduce the critical path. This paper presents and evaluates a new and efficient Montgomery modular multiplication architecture based on a new digit serial computation. The proposed architecture relaxes the high-radix partial multiplication to a binary multiplication. It also performs several multiplications of consecutive zero bits in one clock cycle instead of several clock cycles. Moreover, the right-to-left and left-to-right modular exponentiation architectures have been modified to use the proposed modular multiplication architecture as its structural unit. We provide the implementation results on a Xilinx Virtex 5 FPGA demonstrating that the total computation time and throughput rate of the proposed architectures outperform most results so far in the literatures.

*Index Terms*—Digit serial computation, modular exponentiation, Montgomery modular multiplication, public-key cryptography.

### I. INTRODUCTION

**M**ODULAR multiplication and modular exponentiation are widely used operations in many public-key cryptosystems (PKCs) [1]–[4]. Basically, the modular exponentiation with a large modulus is performed by repeating modular multiplication, which is considerably time-consuming operation [2]. As a result, the performance of many PKCs is entirely depending on the throughput rate of the modular multiplication and the number of required modular multiplications [2]–[4]. The high throughput rate for large integers is hard to achieve without the use of hardware acceleration [2], [4].

Montgomery modular multiplication [5] is an efficient method for the high throughput rate hardware implementation of the modular multiplication with large modulus [6]–[9]. This algorithm replaces the trial division with a series of additions and right shift operations [10], [11]. The challenging issue in the Montgomery modular multiplication [5] is the time-consuming carry propagations of the very large operand addition [2], [10], [12], [13].

The authors are with the Faculty of Electrical and Computer Engineering, Semnan University, Semnan 35131-19111, Iran (e-mail: rezaie@acecr.ac.ir; pkeshavarzi@semnan.ac.ir).

Digital Object Identifier 10.1109/TVLSI.2014.2355854

Several computational techniques and hardware implementations based on the Montgomery modular multiplication have been developed to speed up the modular multiplication which can be classified into three categories: high-radix design [14]–[16], carry–save addition (CSA) design [2], [4], [8], [17]–[26], and systolic array design [27]–[31].

Nevertheless, the use of CSA structure is an efficient approach toward relaxing the problem of time-consuming carry propagation [2], [4], [10]. The challenging issues in the CSA structure are the format conversion from the carrysave representation of the final product to its binary representation, the reduction operation, and the number of required clock cycles. McIvor et al. [18], [19] proposed that the intermediate representation of the multiplier results in the exponentiation is kept in carry-save representation to avoid carry propagation in format conversion at the end of each multiplication [2], [4], [17], [19]. Zhang et al. [8] proposed that the same CSA Montgomery reduction can be used for this format conversion at the expense of multiple cycles overhead. Sutter et al. [4] proposed that fast carry-skip addition can be used for the format conversion and reduction operation to reduce the computation time.

To further improve the performance of Montgomery multipliers, the CSA structure can be combined with other techniques and architectures such as Karatsuba–Ofman [32]–[35] and high radix [4], [10], [12], [13], [36]–[38]. Using high-radix modular multiplication, the number of required clock cycles is reduced at the expense of the critical path overhead [4], [38].

For the modular exponentiation algorithm, the most used approaches are the right-to-left (R2L) and left-to-right (L2R) algorithms. There are several techniques to reduce the number of required modular multiplications in these modular exponentiation algorithms, such as sliding window [39]–[41], signed-digit recoding [42]–[44], and common-multiplicand-multiplication (CMM) [6], [43]–[47].

In this paper, a novel and efficient Montgomery modular multiplication and exponentiation algorithms and their corresponding architectures are developed. The main distinctive characteristics of our contribution are as follows.

- Use a new signed-digit encoding expansion developed in this paper. This new encoding expansion provides multibit-scan technique.

- Relax three operations (the zero chain multiplication, the required additions, and the nonzero digit multiplication)

1063-8210 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received September 7, 2013; revised March 18, 2014, July 5, 2014, and August 20, 2014; accepted August 31, 2014.

2

#### IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS

| Algorithm 1 Radix-2 Montgomery Modular Multiplication<br>Algorithm                                                                                                                                                                  | Algorithm 2 CSA Montgomery Modular Multiplication Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input: X, Y, M;<br>Output: S(n) :=X.Y.R mod M;<br>1. S(0)=0;<br>2. For i=0 To n-1<br>3. $q_i = (S(i)+x_i,Y) \mod 2;$<br>4. $S(i+1) = (S(i)+x_iY+q_i,M)/2;$<br>5. End For<br>6. IF S(n) $\ge$ M Then S(n)=S(n)-M;<br>7. Return S(n); | $eq:started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_st$ |

|                                                                                                                                                                                                                                     | 8. Return S(n);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

to one multibit shift and one binary addition in only one clock cycle.

- 3) Relax the high-radix partial multiplication in each clock cycle to binary multiplication.

- 4) Modify the R2L and L2R modular exponentiation algorithms to utilize the proposed modular multiplication architecture as its structural unit.

- 5) Present the results in the Xilinx Virtex 5 FPGA.

Our implementation results show that the proposed modular multiplication and modular exponentiation architectures have the best performance and throughput rate compared with other modular multiplication and modular exponentiation architectures and outperform most of them in terms of area × time complexity.

The rest of this paper is organized as follows. Section II briefly describes background of the modular multiplication and the modular exponentiation algorithms. Section III presents the proposed architectures. First, the developed encoding expansion and the proposed modular multiplication and its implementation are described, and then the exponentiation algorithm and its implementation are discussed. Section IV provides the complexity analysis and detailed hardware implementation of the developed modular multiplication, and modular exponentiation architectures, and compares results with other architectures. Finally, the conclusion is given in Section V.

### II. BACKGROUND

### A. Montgomery Modular Multiplication

Montgomery modular multiplication algorithm [5] is a widely used modular multiplication algorithm. This algorithm enhances the efficiency of the modular multiplication because it can replace the trial division with the simple right shift and addition operations [6]-[9]. The radix-2 Montgomery modular multiplication for inputs X, Y, and M is shown in Algorithm 1.

The inputs of this algorithm are *n*-bit integers *X*, *Y*, and *M*. The output is  $S(n) := X \cdot Y \cdot R \mod M$ . S(i) represents S in the *i*th iteration,  $x_i \in \{0, 1\}$  denotes the *i*th bit of X, and  $R = 2^{-n} \mod M$ . To eliminate the final comparison and subtraction in step 6 of Algorithm 1, Walter [48] kept the range of S within [0, 2M) by changing the number of iterations and the value of R to n + 2 and  $2^{-(n+2)} \mod M$ , respectively [2], [4], [10]. Although a great hardware complexity can be reduced, the long carry propagation for the very large operand addition still restricts the performance of Algorithm 1 [2], [4], [10]. The main delay time in Algorithm 1 is the long carry

## Algorithm 3 High-Radix CSA Montgomery Modular Multiplication Algorithm

| Input: X, Y, M;                                                                                |  |

|------------------------------------------------------------------------------------------------|--|

| Output: S(n) :=X.Y.R mod M;                                                                    |  |

| 1. Sc(0)=0, Ss(0)=0;                                                                           |  |

| 2. For i=0 to (n/r)-1                                                                          |  |

| 3. $q_i = (Sc(i)+Ss(i)+X^{(i)}Y)(2^{r+1}-M_{r,0}^{-1}) \mod 2^r$ ;                             |  |

| 4. (Sc(i+1), Ss(i+1)) =(Ss(i)+Sc(i)+X <sup>(i)</sup> .Y +q <sup>(i)</sup> .M)/2 <sup>r</sup> ; |  |

| 5. End for                                                                                     |  |

| 6. S(n)=Sc(n)+Ss(n);                                                                           |  |

| 7. IF S(n)≥M Then S(n)=S(n)-M;                                                                 |  |

|                                                                                                |  |

8. Return S(n);

propagation delay. This problem can be solved using CSA [2], [4], [10]. The CSA version of the Montgomery modular multiplication is shown in Algorithm 2.

In this algorithm, Sc and Ss denote the carry and sum components of S. The challenging issues in this algorithm are the format conversion from the carry-save representation of the final product to its binary representation in step 6, the reduction operation in step 7, and the number of required clock cycles. Recently, Sutter et al. [4] proposed that a fast carry-skip addition can be used for performing steps 6 and 7 to enhance the efficiency of the CSA Montgomery modular multiplication.

Another way to enhance the efficiency of the CSA Montgomery modular multiplication is combination of CSA architecture with other techniques such as high radix [10], [13], [36], [37]. In this approach, a group of multiplier bits are processed at each clock cycle instead of several clock cycles. Algorithm 3 shows the high-radix CSA Montgomery modular multiplication algorithm.

In this algorithm,  $X^{(i)}$  denotes the *i*th digit of X and  $M_{r,..0} = M \mod 2^{r+1}$ . This algorithm reduces the number of required clock cycles from n-clock cycle to n/r-clock cycle for radix- $2^r$  at the expense of the critical path overhead. The critical path includes  $X^{(i)} \cdot Y$  and  $q^{(i)} \cdot M$  computations. In our architecture, we relax the high-radix  $X^{(i)} \cdot Y$  multiplication to binary multiplication and improve the  $q^{(i)} \cdot M$  computation.

### **B.** Modular Exponentiation

The modular exponentiation algorithm usually consists of a repetition of modular multiplication algorithm [4], [38], [39], [49]. This algorithm is typically implemented

REZAI AND KESHAVARZI: HIGH-THROUGHPUT MODULAR MULTIPLICATION AND EXPONENTIATION ALGORITHMS

| Algorithm 4 L2R Modular Exponentiation Algorithm |                      |

|--------------------------------------------------|----------------------|

| -<br>Input: N, M, E;                             | Input:               |

| Output: C :=M <sup>E</sup> mod N;                | Outpu                |

| {pre-computation phase}                          | 1. c <sub>0</sub> := |

| 1. M*=Mont(M, R <sup>2</sup> , N);               | 2. For               |

| 2. S=R mod N;                                    | 3. c <sub>i</sub> .  |

| {exponentiation phase}                           | 4. d                 |

| 3. For i=k <sub>e</sub> -1To 0                   | 5. Reti              |

| 4. S=Mont (S, S, N);                             |                      |

| 5. If (e <sub>i</sub> =1) Then S=Mont(M*, S, N); |                      |

| 6. End for                                       |                      |

| {Post-computation phase}                         | <i>C. C</i>          |

| 7. C=Mont(S, 1, N);                              | А                    |

| 8. Return C;                                     | (r                   |

| Algorithm 5 R2L Modula | r Exponentiation Algorithm |

|------------------------|----------------------------|

|------------------------|----------------------------|

Input: N, M, E; Output: C :=M<sup>E</sup> mod N; {pre-computation phase} 1. M\*=Mont(M, R<sup>2</sup>, N); 2. S=R mod N; {exponentiation phase} 3. For i= 0 To  $k_e$ -1 4. If (ei=1) Then S=Mont(M\*, S, N); 5. M\*=Mont (M\*, M\*, N); 6. End for {Post-computation phase} 7. C=Mont(S, 1, N); 8. Return C;

using the binary methods and the Montgomery modular multiplication algorithm. There are two basic algorithms in the binary methods: the L2R and R2L modular exponentiation algorithms. If the Montgomery modular multiplication is used in the modular exponentiation algorithm, the additional preprocessing and postprocessing steps are required for converting the operands to the Montgomery domain [2], [4].

The L2R modular exponentiation algorithm used for computing  $C = M^E \mod N$  is summarized in Algorithm 4 where M < N denotes an *n*-bit massage, *E* denotes a  $k_e$ -bit exponent, and *N* denotes an *n*-bit modulus.

In this algorithm, the value of R is  $2^{-n}$  or  $2^{-(n+2)}$  depending on the modular multiplication algorithm described in Section II-A. The exponent bits are scanned from the most significant bit (MSB) and there exists data dependency between the square and multiplication operations. This algorithm requires  $1.5k_e + 2$  multiplication operations on average to perform the modular exponentiation algorithm [2], [4].

Another way to compute  $C = M^E \mod N$ , the R2L modular exponentiation algorithm, processes the exponent bits from the least significant bit (LSB). This algorithm is summarized in Algorithm 5.

In this algorithm, there is no data dependency between the multiplication and square operations. In other words, two operations can execute in parallel. Therefore, the total computation time is reduced at the expense of area overhead. This algorithm requires  $k_e + 2$  multiplication operations to perform the modular exponentiation algorithm [2], [4].

| Algorithm | 6 Canonical Recoding Algorithm |  |

|-----------|--------------------------------|--|

|           |                                |  |

| Input: $X = (x_{n-1}x_{n-2}x_1x_0)_2$                    |

|----------------------------------------------------------|

| Output: $X_{CR} = (d_{n-1}d_{n-2}d_1d_0)_{SD}$           |

| 1. c <sub>0</sub> := 0;                                  |

| 2. For i = 0 to n-1                                      |

| 3. $c_{i+1} := \lfloor (x_i + x_{i+1} + c_i)/2 \rfloor;$ |

| 4. $d_i := x_i + c_i - 2c_{i+1};$                        |

| 5. Return X <sub>cR</sub> ;                              |

### C. Canonical Recoding (CR) Algorithm

A canonical representation [50] of an integer  $X_{CR} = (x_{n-1}x_{n-2}...x_1x_0)$  is a sequence of digit such that  $x_i \in \{-1, 0, 1\}$ . This representation is one of the existing signed-digit representations with unique features that make it useful in high-speed arithmetic [51], [52]. Algorithm 6 is used for converting an *n*-bit integer X from the binary representation to its canonical representation.

In this algorithm, the input integer X is processed from the LSB to MSB. The average Hamming weight of an *n*-bit canonical recoded integer is n/3 [42], [51]. In the hardware implementation, several bits can be processed simultaneously [51], which enhance the efficiency of the implementation of canonical recoding algorithm [51].

### **III. PROPOSED ALGORITHM AND ARCHITECTURE**

The design objectives in this paper are speeding up the modular multiplication and modular exponentiation algorithms. The design strategy is using the multibit-scanmultibit-shift technique in one clock cycle. In the proposed modular multiplication algorithm, the high-radix computation of  $X^{(i)} \cdot Y$  becomes the binary multiplication. The proposed algorithm also executes several addition operations, required for zero chain, in one clock cycle instead of several clock cycles. Therefore, we consider the reformulation of the Montgomery modular multiplication algorithm and then, map the results to derive a modular exponentiation algorithm. This reformulation of modular multiplication is based on a new multiplier expansion developed in this paper.

### A. Proposed Integer Expansion

A proposed expansion of an *n*-bit integer X is defined here as  $X_{SD} = (z_{n-1}z_{n-2}...z_1z_0)$ . Each digit of the proposed expansion,  $z_i$ , includes a number of consecutive zero bits that can be followed by a nonzero digit or a coefficient. In other words, each digit of the proposed expansion,  $z_i$ , includes a pair  $(k_i, f^{(i)})$ , where  $f^{(i)}$  denotes the number of zero bits in sequence, and  $k_i$  denotes the coefficient.

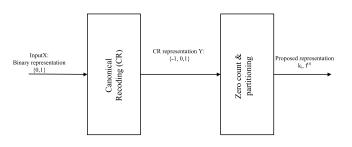

The proposed expansion of an integer X is computed by applying Algorithm 6 and the partitioning method [39], [40] to the binary representation of the integer X. The canonical recoding is utilized to enhance the probability of zero bits in the proposed integer expansion and thereby reducing the number of required digits in the proposed integer expansion.

Note that all digits should have an equal size in the hardware implementation. As a result, the number of zero bits in sequence in each digit of the proposed integer expansion will

Fig. 1. Block diagram for converting an integer X from binary representation to the proposed integer expansion.

TABLE I

POSSIBLE CONDITIONS FOR y<sub>i</sub>

| yi | $\mathcal{Y}_i^s$ | $y_i^d$ |

|----|-------------------|---------|

| 0  | 0                 | 0       |

| 1  | 0                 | 1       |

| -1 | 1                 | 0       |

be limited to  $\ell$ . Our analysis shows that, regarding hardware limitations, the optimal value for  $\ell$  is 2, two consecutive zero bits followed by nonzero digit or three consecutive zero bits.

For example, the proposed expansion of  $X = (254855)_{10} = (111110001110000111)_2$  is computed as follows.

After applying the canonical recoding, it is shown as  $X_{\text{CR}} = (10000\bar{1}00100\bar{1}000100\bar{1})_{\text{CR}}$ , after applying the partitioning method with  $\ell = 2$ , it is shown as  $(10)(000)(\bar{1}00)(100)(\bar{1})(000)(100)(\bar{1})$ , and finally the proposed expansion is shown as  $(1, 1)(0, 3)(\bar{1}, 2)(1, 2)(\bar{1}, 0)(0, 2)(1, 2)(\bar{1}, 0)$ .

When this expansion is utilized in the Montgomery modular multiplication, it results in a series of binary partial multiplications and multiplits. More specifically,  $k_i$  is utilized for binary partial multiplication, and  $f^{(i)}$  is utilized for multiplit shift.

In hardware implementation, each pair of the proposed expansion is represented by three bits: one bit for  $k_i$  and two bits for  $f^{(i)}$ .  $k_i$  is as follows:

$$k_i = \begin{cases} 0, & \text{for positive integers} \\ 1, & \text{for negative integers.} \end{cases}$$

However, when  $f^{(i)} = 3$ ,  $k_i$  is zero, and it denotes the coefficient is zero. Therefore, the hardware representation for the proposed integer expansion is as follows:

000, 011, 110, 011, 100, 011, 011, 100.

Fig. 1 shows two major steps for converting the binary representation to the proposed integer expansion.

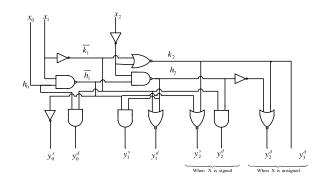

In the CR implementation, each digit  $y_i$  contains two bits  $\{y_i^s, y_i^d\}$ . Table I defines all possible conditions for  $y_i$ .

Fig. 2 shows the schematic circuit for converting an integer from its binary representation into its CR representation.

Note that this schematic circuit is proposed prior to this paper in [51]. The partitioning and zero count strategy used in this paper is as follows.

| Algorithm 7 Partitioning and Zero Count Strategy              |  |

|---------------------------------------------------------------|--|

| Input: X <sub>CR</sub> ;                                      |  |

| Output: X <sub>sD</sub> (k <sub>i</sub> , f <sup>(i)</sup> ); |  |

| d=0, i=0;                                                     |  |

| Sp: Check the incoming signal digit;                          |  |

| IF it is not zero Then                                        |  |

| IF it is 01 Then k <sub>i</sub> =0;                           |  |

| Else k <sub>i</sub> =1;                                       |  |

| f <sup>(i)</sup> =d, i=i+1;                                   |  |

| d=0;                                                          |  |

| go to SP;                                                     |  |

| Else                                                          |  |

| d=d+1;                                                        |  |

| IF d is equal with 3 Then                                     |  |

| k <sub>i</sub> =0, f <sup>(i)</sup> =d, i=i+1;                |  |

| d=0;                                                          |  |

| go to SP:                                                     |  |

Fig. 2. Circuit used for converting an integer from its binary representation *X* to the CR representation  $Y = \{y_n, y_{n-1}, \dots, y_1, y_0\}$ .

### B. Proposed Modular Multiplication

In Algorithm 3, r bits of the multiplier are processed per iteration. The drawback of using Algorithm 3 is that each digit of  $q^{(i)}$  and  $X^{(i)}$  are represented in radix-2<sup>*r*</sup>.

The corresponding version that relaxes the high-radix partial multiplication  $X^{(i)}$  Y to the binary multiplication is the proposed variable length Montgomery modular multiplication (VLM3) algorithm that is shown in Algorithm 8. The inputs of this algorithm are  $X_{SD}$ , Y, and M, which denote the proposed expansion of multiplier X, the *n*-bit multiplicand, and modulus, respectively. Pc and Ps denote the carry and sum components of P.

This new modular multiplication algorithm relaxes the highradix partial multiplication  $X^{(i)} \cdot Y$  to binary modular multiplication using the proposed expansion. In other words, applying the proposed expansion to the multiplier, the computation of  $(Pc(i), Ps(i)) = Sc(i) + Ss(i) + X^{(i)} \cdot Y$  is relaxed to

$$(Pc(i), Ps(i)) = Sc(i) + Ss(i) + 2^{a^{(i)}} \cdot Y$$

(Pc(i), Ps(i)) = Sc(i) + Ss(i) - 2^{a^{(i)}} \cdot Y

or

# (Pc(i), Ps(i)) = Sc(i) + Ss(i)

based on  $f^{(i)} \neq 3$  and  $k_i = 0$ ,  $f^{(i)} \neq 3$  and  $k_i = 1$ , or  $f^{(i)} = 3$  in steps 6, 7, and 4, respectively. These steps can be implemented using a multiplexer (Mux), a modified (limited number of shifts) Barrel shifter (MBS), and LUTs.

REZAI AND KESHAVARZI: HIGH-THROUGHPUT MODULAR MULTIPLICATION AND EXPONENTIATION ALGORITHMS

# Algorithm 8 Proposed Modular Multiplication Algorithm (VLM3 Algorithm)

Input: X<sub>SD</sub>(k<sub>i</sub>, f<sup>(i)</sup>),Y, M;

Output: S=X.Y.2<sup>-n</sup> mod M;

1. Sc(0)=0, Ss(0)=0;

- 2. For i=0 to J /\* J shows the number of digits in the proposed expansion\*/

- 3.  $a^{(i)} = f^{(i)}$ 4. If  $f^{(i)} = 3$  Then  $(P_c(i), P_s(i)) := S_c(i) + S_s(i), a^{(i)} = a^{(i)} - 1;$

- 5. Else

- 6. If  $k_i = 0$  Then  $(P_c(i), P_s(i)) := S_c(i) + S_s(i) + 2^{a^{(i)}} \cdot Y$ ;

- 7. Else ( $P_c(i)$ ,  $P_s(i)$ ) :=  $S_c(i)+S_s(i)-2^{a^{(i)}}$ . Y;

- 8.  $q_i = ((P_c(i) + P_s(i))_{k \dots 0}) (2^{a^{(i)}+1} M_{k 0}^{-1}) \mod 2^{a^{(i)}+1};$

- 9.  $(S_{c}(i+1),S_{s}(i+1))=(P_{c}(i) + P_{s}(i) + q^{(i)}M)/2^{a^{(i)}+1};$

- 10. End for;

- 11.  $S(n)=S_s(J+1) + S_c(J+1);$

- 12. If  $S(n) \ge M$  Then S(n) := S(n) M;

- 13. Return S(n);

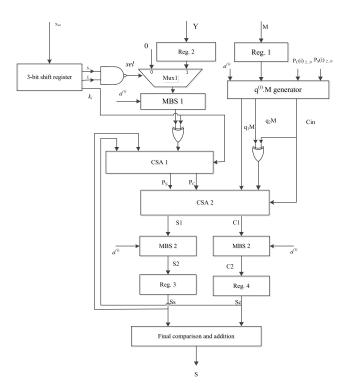

Fig. 3. Data path of a basic cell of the VLM3 algorithm.

Moreover, this new modular multiplication algorithm executes several addition operations of consecutive zero bits in one clock cycle instead of several clock cycles. This operation is executed in step 9, which is implemented using the MBS and CSAs.

The format conversion from the carry-save representation of the final product into its binary representation and reduction operation, steps 11 and 12 in Algorithm 7, are implemented similar to [4] using two carry-skip adders and a multiplexer. This solution required *w* cycles to perform these steps, where  $w = \lceil T/t \rceil$ , *T* denotes the period of circuit without final addition, and *t* is the sum of addition delay and multiplexer delay. Fig. 3 shows the data path of a basic cell that implements the VLM3 algorithm.

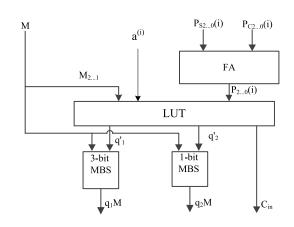

Fig. 4. Proposed architecture for the  $q^{(i)} \cdot M$  generator.

The proposed architecture contains three MBSs, two CSAs, four registers, a 3-bit shift register, a Mux, two XORs, a NAND gate, a  $q^{(i)} \cdot M$  generator, and final comparison and addition block.

In this circuit, the sel signal of Mux1 is determined based on the  $f^{(i)}$  as follows:

sel =

$$\begin{cases} 0, & \text{where } f^{(i)} = 3\\ 1, & \text{where } f^{(i)} \neq 3. \end{cases}$$

In this case, sel = 0 provides zero and sel = 1 provides *Y* for MBS1 input. Moreover, the  $k_i$  signal is utilized to determine that the CSA1 works as an adder or a substructure. In other words, the CSA1 provides  $Sc(i) + Ss(i) + X^{(i)} \cdot Y$  in each clock cycle, the CSA2 provides  $Pc(i) + Ps(i) + q^{(i)} \cdot M$ , and the MBSs shift the inputs based on the value of  $a^{(i)}$ .

To compute  $q^{(i)} \cdot M$ , a LUT and two MBSs are utilized. For  $a^{(i)} = 2$ , the coefficient  $q^{(i)}$  depends on the least three bits of the partial results of CSA1, Pc, and Ps, and two bits of  $M, m_2$ , and  $m_1$ . The implementation of  $q^{(i)} \cdot M$  is as follows. First, splitting  $q^{(i)}$  into two numbers that are power of 2,  $q_1$  and  $q_2$ . Second, shifting M to get two components of  $q^{(i)} \cdot M$ ,  $q_1 \cdot M$  and  $q_2 \cdot M$ , based on  $q_1$  and  $q_2$ . Finally, adding these two components with (Pc(i), Ps(i)) using CSA2.

For example with  $q^{(i)} = 6$ ,  $q^{(i)}$  can be split into  $q_1 = 4$  and  $q_2 = 2$  or  $q_1 = 8$ , and  $q_2 = -2$ . Then, 6M can be replaced as 4M + 2M or 8M - 2M. Note that the negative component, for example -2M in the previous example, is implemented by inverting the positive component, 2M, and introducing a carryin with the value of 1. As a result, only one of the components can be chosen as a negative value. Fig. 4 shows the proposed architecture of the  $q^{(i)} \cdot M$  generator. The proposed architecture contains a 3-bit full adder (FA), a LUT, a 1-bit MBS, and a 3-bit MBS. The LUT outputs are performed according to Tables II–IV. Note that for  $a^{(i)} = 0$ , the  $q^{(i)} = P_0(i)$ .

In Table IV, the  $q'_i$  shows the number of required shifts, i.e.,  $q_i = 2^{q'_i}$ . The LUT outputs,  $q'_1$  and  $q'_2$ , are the control signals for the MBSs that implement  $q_1 \cdot M$  and  $q_2 \cdot M$ . The LUT also has an output  $C_{in}$  which is asserted 1 whenever  $q_2 \cdot M$  is negative. This signal becomes a carry-in for the CSA2 in Fig. 3. IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS

TABLE II LUT FOR DETERMINING  $q^{(i)}$  for  $a^{(i)} = 2$

| D (i)                 | $m_2 m_1$ |    |    |    |

|-----------------------|-----------|----|----|----|

| P <sub>20</sub> (i) - | 00        | 01 | 10 | 11 |

| 000                   | 0         | 0  | 0  | 0  |

| 001                   | 7         | 5  | 3  | 1  |

| 010                   | 6         | 2  | 6  | 2  |

| 011                   | 5         | 7  | 1  | 3  |

| 100                   | 4         | 4  | 4  | 4  |

| 101                   | 3         | 1  | 7  | 5  |

| 110                   | 2         | 6  | 2  | 6  |

| 111                   | 1         | 3  | 5  | 7  |

TABLE III LUT for Determining  $q^{(i)}$  for  $a^{(i)} = 1$

| P <sub>10</sub> (i) | m <sub>1</sub> |   |

|---------------------|----------------|---|

| 1 10(1)             | 0              | 1 |

| 00                  | 0              | 0 |

| 01                  | 3              | 1 |

| 10                  | 2              | 2 |

| 11                  | 1              | 3 |

TABLE IV LUT FOR DETERMINING THE COMPONENTS OF  $q^{(i)}$

| $q^{\scriptscriptstyle (i)}$ | $q_{_1}$ | $q_1^{'}$ | $q_{_2}$ | $q_2$ | $C_{in}$ |

|------------------------------|----------|-----------|----------|-------|----------|

| 0                            | 1        | 0         | -1       | 0     | 1        |

| 1                            | 2        | 1         | -1       | 0     | 1        |

| 2                            | 1        | 0         | 1        | 0     | 0        |

| 3                            | 2        | 1         | 1        | 0     | 0        |

| 4                            | 2        | 1         | 2        | 1     | 0        |

| 5                            | 4        | 2         | 1        | 0     | 0        |

| 6                            | 4        | 2         | 2        | 1     | 0        |

| 7                            | 8        | 3         | -1       | 0     | 1        |

# Algorithm 9 Proposed R2L Modular Exponentiation Algorithm

| $eq:spectral_set_set_set_set_set_set_set_set_set_set$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input: N, M, E;<br>Output: C :=M <sup>E</sup> mod N;                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| <ol> <li>Convert R<sup>2</sup> and 1 from binary representation to the proposed expansion, R<sup>2</sup><sub>so</sub>, 1<sub>so</sub>;</li> <li>S=R mod N;</li> <li>M*=VLM3(M, R<sup>2</sup><sub>so</sub>, N);</li> <li>Convert M* from binary representation to the proposed expansion, M<sub>so</sub>.<br/>{exponentiation phase}</li> <li>For i=OTo k<sub>e</sub>-1</li> <li>If (e<sub>i</sub>=1) Then S=VLM3 (S, M<sub>so</sub>, N);</li> <li>M*=VLM3(M*,M<sub>so</sub>, N);</li> <li>Convert M* from binary representation to the proposed expansion, M<sub>so</sub>.</li> <li>End for;</li> <li>Post-computation}</li> <li>C=VLM3(S, 1<sub>so</sub>, N);</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • •                                                                                   |

| <ul> <li>3. M*=VLM3(M, R<sup>2</sup><sub>SD</sub>, N);</li> <li>4. Convert M* from binary representation to the proposed expansion, M<sub>SD</sub>. {exponentiation phase}</li> <li>5. For i=OTo k<sub>e</sub>-1</li> <li>6. If (e<sub>i</sub>=1) Then S=VLM3 (S, M<sub>SD</sub>, N);</li> <li>7. M*=VLM3(M*,M<sub>SD</sub>, N);</li> <li>8. Convert M* from binary representation to the proposed expansion, M<sub>SD</sub>.</li> <li>9. End for;</li> <li>{Post-computation}</li> <li>10. C=VLM3(S, 1<sub>SD</sub>, N);</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                       |

| <ul> <li>4. Convert M* from binary representation to the proposed expansion, M<sub>SD</sub>. {exponentiation phase}</li> <li>5. For i=OTo k<sub>e</sub>-1</li> <li>6. If (e<sub>i</sub>=1) Then S=VLM3 (S, M<sub>SD</sub>, N);</li> <li>7. M*=VLM3(M*,M<sub>SD</sub>, N);</li> <li>8. Convert M* from binary representation to the proposed expansion, M<sub>SD</sub>.</li> <li>9. End for;</li> <li>{Post-computation}</li> <li>10. C=VLM3(S, 1<sub>SD</sub>, N);</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2. S=R mod N;                                                                         |

| eq:space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space-space- | 3. M*=VLM3(M, R <sup>2</sup> <sub>SD</sub> , N);                                      |

| 5. For i=0To $k_e$ -1<br>6. If (e <sub>i</sub> =1) Then S=VLM3 (S, M <sub>SD</sub> , N);<br>7. M*=VLM3(M*,M <sub>SD</sub> , N);<br>8. Convert M* from binary representation to the proposed expansion, M <sub>SD</sub> .<br>9. End for;<br>{Post-computation}<br>10. C=VLM3(S, 1 <sub>SD</sub> , N);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4. Convert $M^*$ from binary representation to the proposed expansion, $M_{SD}$ .     |

| <ul> <li>6. If (e<sub>i</sub>=1) Then S=VLM3 (S, M<sub>SD</sub>, N);</li> <li>7. M*=VLM3(M*,M<sub>SD</sub>, N);</li> <li>8. Convert M* from binary representation to the proposed expansion, M<sub>SD</sub>.</li> <li>9. End for;</li> <li>{Post-computation}</li> <li>10. C=VLM3(S, 1<sub>SD</sub>, N);</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | {exponentiation phase}                                                                |

| <ol> <li>M*=VLM3(M*,M<sub>SD</sub>, N);</li> <li>Convert M* from binary representation to the proposed expansion, M<sub>SD</sub>.</li> <li>End for;<br/>{Post-computation}</li> <li>C=VLM3(S, 1<sub>SD</sub>, N);</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5. For i=0To k <sub>e</sub> -1                                                        |

| <ol> <li>Convert M* from binary representation to the proposed expansion, M<sub>SD</sub>.</li> <li>End for;<br/>{Post-computation}</li> <li>C=VLM3(S, 1<sub>SD</sub>, N);</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6. If (e <sub>i</sub> =1) Then S=VLM3 (S, M <sub>SD</sub> , N);                       |

| 9. End for;<br>{Post-computation}<br>10. C=VLM3(S, 1 <sub>SD</sub> , N);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7. M*=VLM3(M*,M <sub>SD</sub> , N);                                                   |

| {Post-computation}<br>10. C=VLM3(S, 1 <sub>SD</sub> , N);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8. Convert M* from binary representation to the proposed expansion, M <sub>SD</sub> . |

| 10. C=VLM3(S, 1 <sub>sD</sub> , N);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9. End for;                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | {Post-computation}                                                                    |

| 11 Return C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10. C=VLM3(S, 1 <sub>SD</sub> , N);                                                   |

| II. Actum C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11. Return C;                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Е                                                                                     |

### C. Proposed Modular Exponentiation

The sliding window method and CMM method required extra area [4], [47]. As a result, these methods are interesting ideas for software or software/hardware implementations [4], [39], [47], in which the extra area is not a problem. In this paper, R2L and L2R modular exponentiation algorithms are implemented using VLM3 algorithm. Since, a new integer expansion is utilized in the VLM3 algorithm, the R2L and L2R modular exponentiation algorithms need to be modified to utilize the VLM3 algorithm as its structural unit.

The proposed R2L modular exponentiation algorithm, which employs the VLM3 algorithm, is shown in Algorithm 9. In this algorithm,  $R = 2^{-n}$ ,  $R_{SD}$  and  $M_{SD}$  denote R and  $M^*$  in the proposed integer expansion, respectively. The format conversion from binary representation of  $R^2$  and 1 to the proposed integer expansion is precomputed because these values are fixed.

The format conversion of  $M^*$ , in steps 4 and 8 of Algorithm 9, is executed in parallel with previous multiplication. These steps are executed after one multiplication delay compared with its previous step. As a result, the format

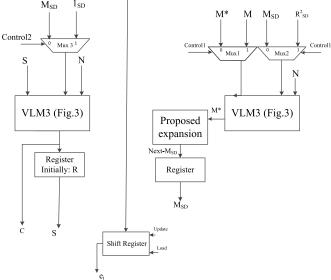

Fig. 5. Proposed R2L modular exponentiation architecture.

conversion in this algorithm reasonably affects the computation time. The proposed R2L modular exponentiation architecture is shown in Fig. 5.

In the architecture of Fig. 5, the signal Control1 is utilized to control the execution of steps 3 and 7 of Algorithm 9. Control1 = 1 is utilized to perform step 3, and Control1 = 0 is utilized to perform step 7. The signal Control2 is also utilized to control the execution of steps 6 and 10 of Algorithm 9. Control2 = 0 is utilized to perform step 6, and Control2 = 1 is utilized to perform step 10. Moreover, both multiplication and square operations are executed in parallel. The total computation time is approximately expressed as  $T = (k_e + 4)T_{MP}$ , where  $T_{MP}$  denotes the multiplication time.

The proposed L2R modular exponentiation algorithm, which employs the VLM3 algorithm, is shown in Algorithm 10. The format conversion in this algorithm also reasonably affects the computation time.

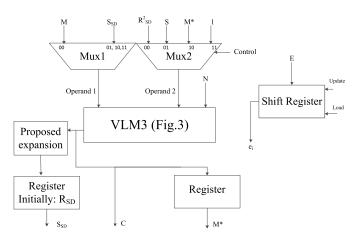

The proposed L2R modular exponentiation architecture is shown in Fig. 6.

| Algorithm | 10 | Proposed | L2R | Modular | Exponentiation |

|-----------|----|----------|-----|---------|----------------|

| Algorithm |    |          |     |         |                |

| Input: N, M, E;                                                                      |

|--------------------------------------------------------------------------------------|

| Output: C :=M <sup>E</sup> mod N;                                                    |

| {pre-computation phase}                                                              |

| 1. Convert R from binary representation to the proposed expansion, $R_{\text{sd}}$ ; |

| 2. S= R <sub>sD</sub> ;                                                              |

| 3. M*=VLM3(M, R <sup>2</sup> <sub>SD</sub> , N);                                     |

| {exponentiation phase}                                                               |

| 4. For i=k <sub>e</sub> -1To 0                                                       |

| 5. S=VLM3 (S, S <sub>SD</sub> , N);                                                  |

| 6. Convert S from binary representation to the proposed expansion, S <sub>SD</sub> . |

| 7. If (e <sub>i</sub> =1) Then                                                       |

| 8. S=VLM3(M*, S <sub>SD</sub> , N);                                                  |

| 9. Convert S from binary representation to the proposed expansion, S <sub>SD</sub> . |

| 10. End lf;                                                                          |

| 11. End for;                                                                         |

| {Post-computation}                                                                   |

| 12. C=VLM3(1, S <sub>SD</sub> , N);                                                  |

| 13. Return C;                                                                        |

|                                                                                      |