**Chapter 1**

## Introduction

Addison-Wesley is an imprint of

FIGURE 1.7 Silicon lattice and dopant atoms

p-type n-type

Anode Cathode

#### FIGURE 1.8

p-n junction diode structure and symbol

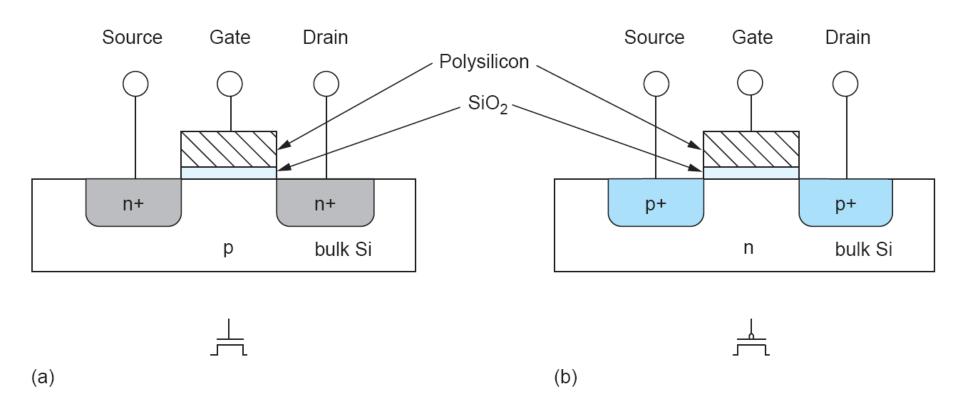

FIGURE 1.9 nMOS transistor (a) and pMOS transistor (b)

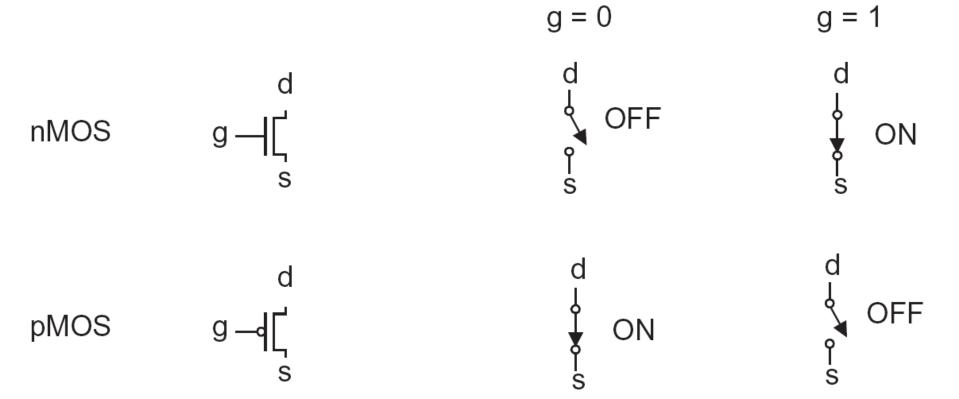

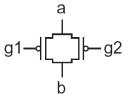

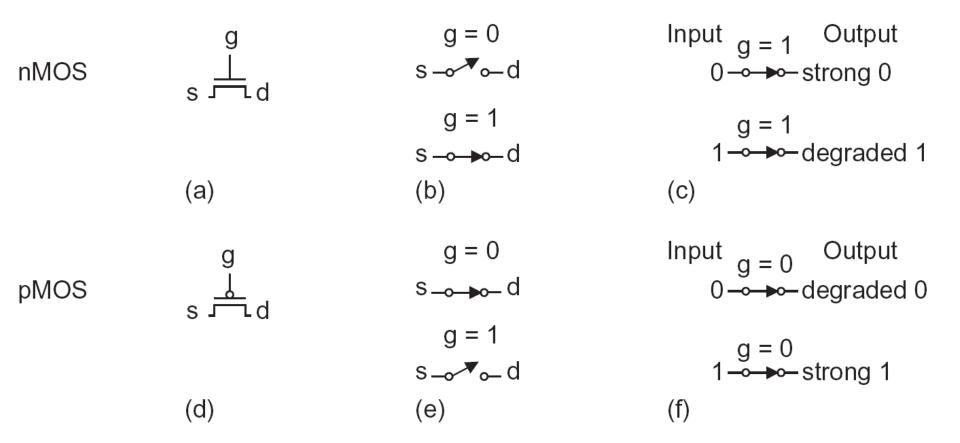

FIGURE 1.10 Transistor symbols and switch-level models

(a)

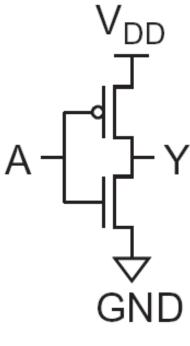

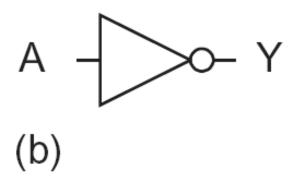

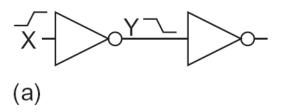

#### **FIGURE 1.11**

Inverter schematic (a) and symbol

(b)

$$Y = \overline{A}$$

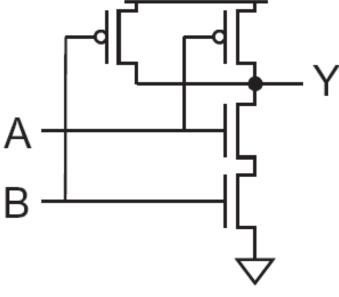

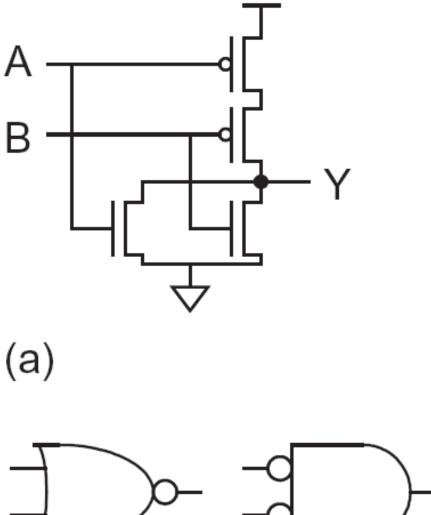

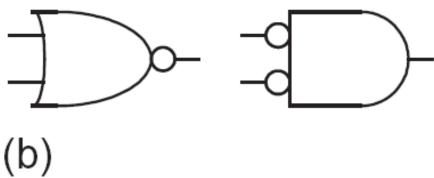

**FIGURE 1.12** 2-input NAND gate schematic (a) and symbol (b)  $Y = \overline{A \cdot B}$

(a)

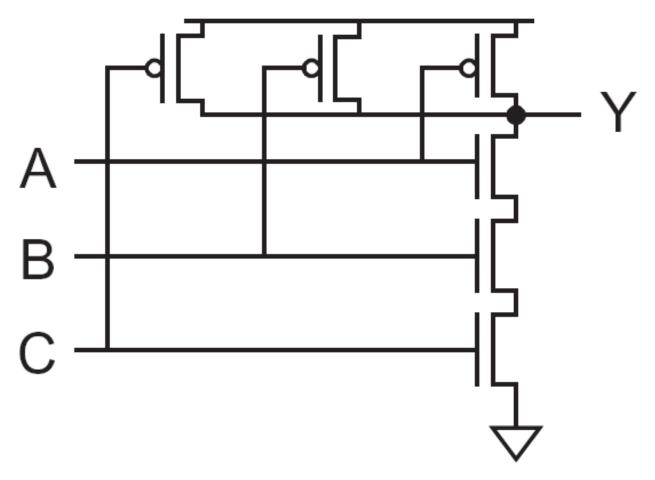

**FIGURE 1.13** 3-input NAND gate schematic  $Y = \overline{A \cdot B \cdot C}$

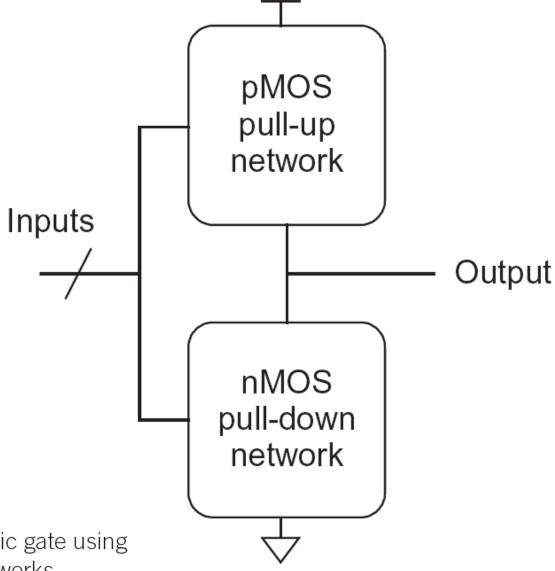

**FIGURE 1.14** General logic gate using pull-up and pull-down networks

OFF

OFF

OFF

ON

ON

OFF

OFF

OFF

(c)

OFF

ON

ON

ON

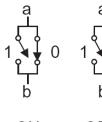

#### **FIGURE 1.15**

Connection and behavior of series and parallel transistors

(d)

ON

ON

ON

OFF

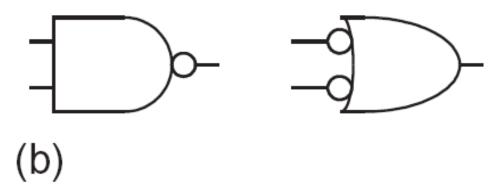

**FIGURE 1.16** 2-input NOR gate schematic (a) and symbol (b)  $Y = \overline{A + B}$

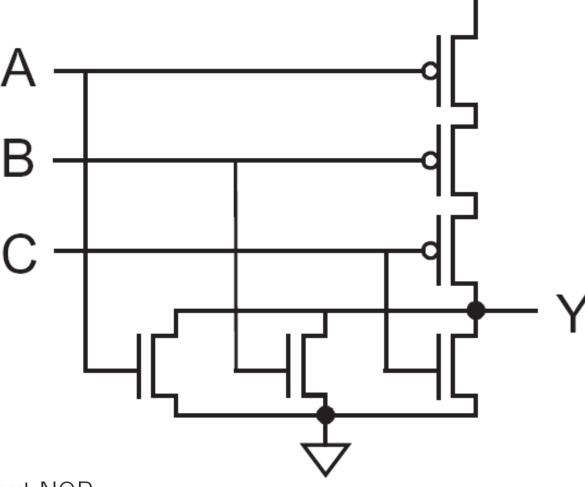

**FIGURE 1.17** 3-input NOR gate schematic  $Y = \overline{A + B + C}$

**FIGURE 1.18** CMOS compound gate for function  $Y = (A \cdot B) + (C \cdot D)$

### **FIGURE 1.19**

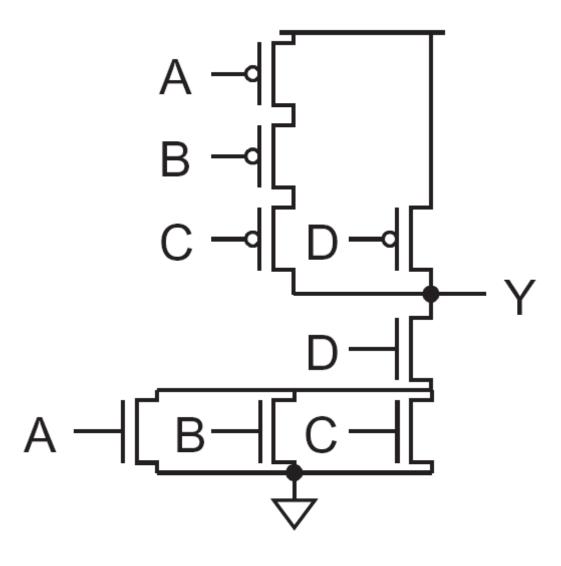

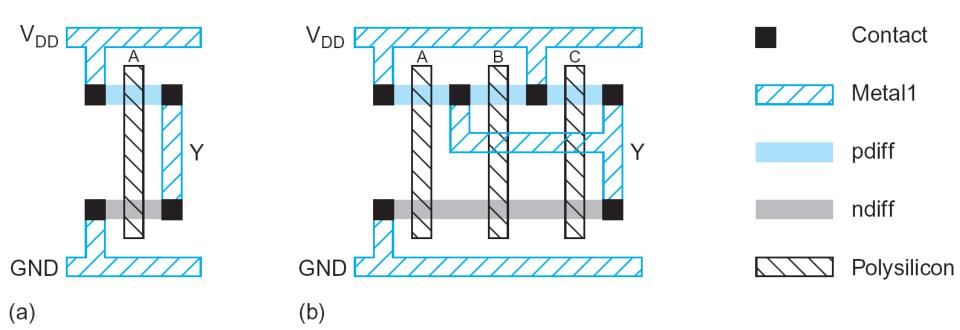

CMOS compound gate for function  $Y = (\overline{A + B + C}) \cdot \overline{D}$

FIGURE 1.20 Pass transistor strong and degraded outputs

$$g = 0$$

,  $gb = 1$

$a \multimap b$

$g = 1$ ,  $gb = 0$

$a \multimap b$

(b)

Input Output

$$g = 1, gb = 0$$

$$0 \longrightarrow strong 0$$

$$g = 1, gb = 0$$

$$1 \longrightarrow strong 1$$

(c)

(d)

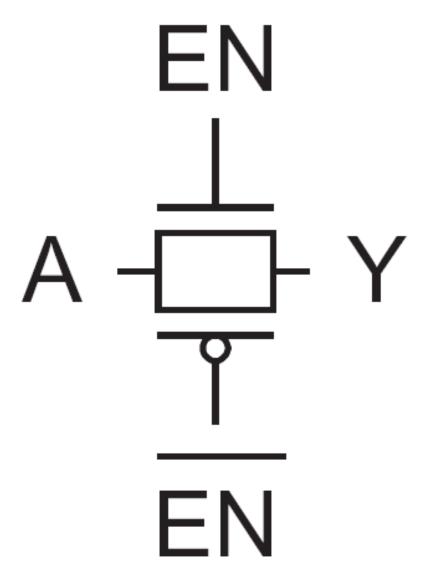

### FIGURE 1.21 Transmission gate

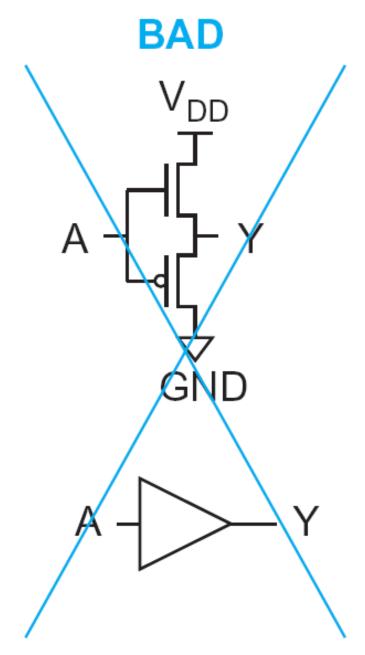

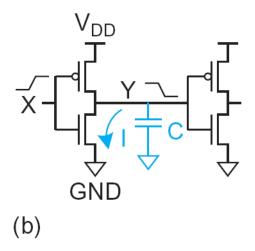

**FIGURE 1.22**

Bad noninverting buffer

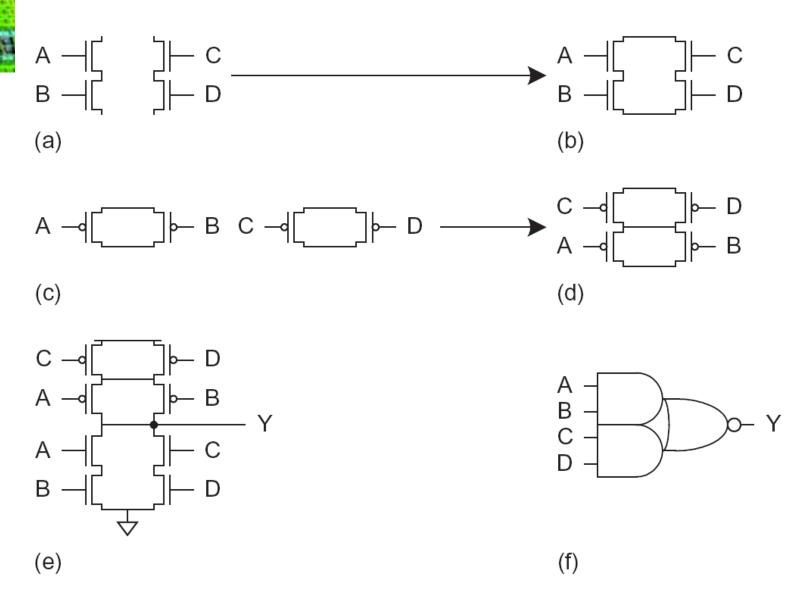

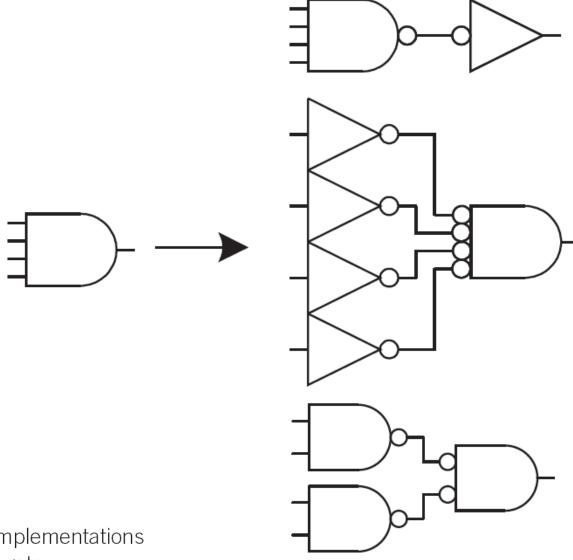

**FIGURE 1.23** Various implementations of a CMOS 4-input AND gate

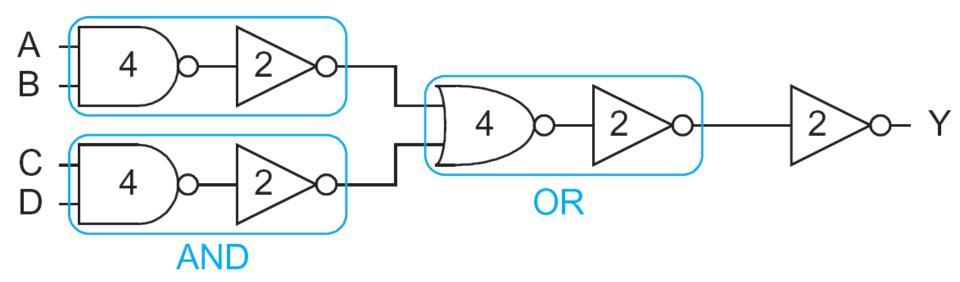

**FIGURE 1.24** Inefficient discrete gate implementation of AOI22 with transistor counts indicated

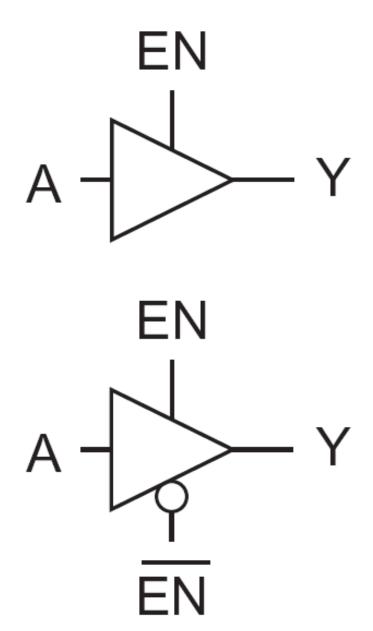

# FIGURE 1.25 Tristate buffer symbol

**FIGURE 1.26**

Transmission gate

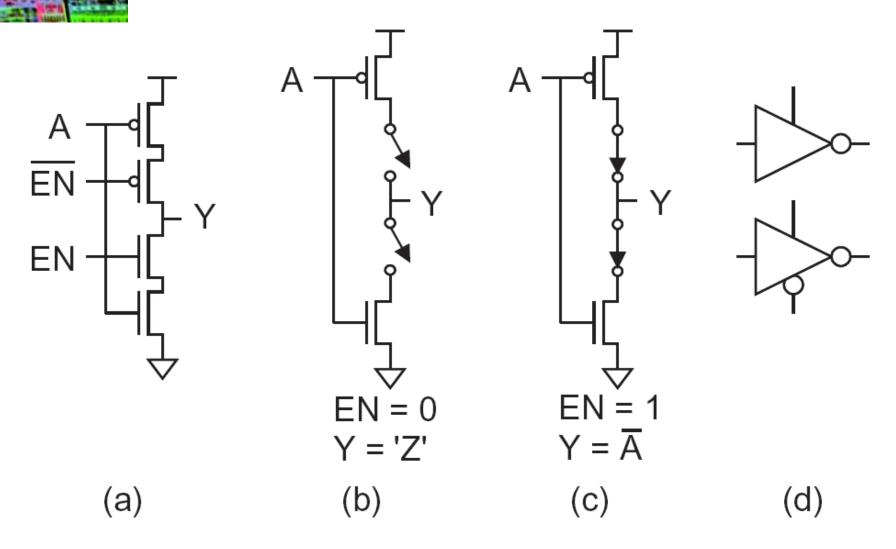

FIGURE 1.27 Tristate Inverter

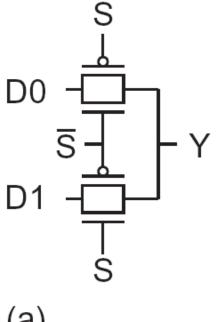

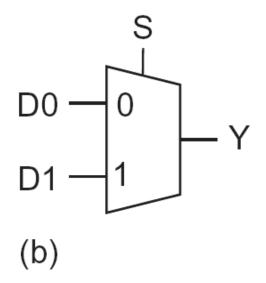

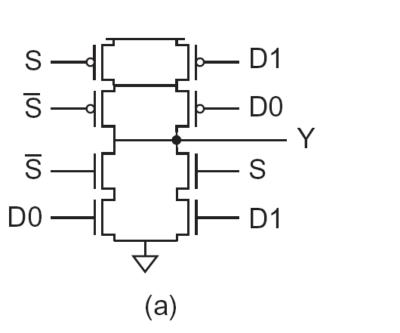

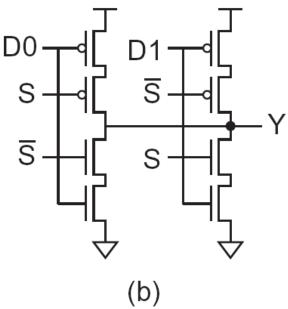

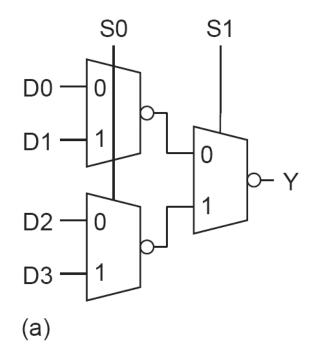

FIGURE 1.28 Transmission gate multiplexer

(a)

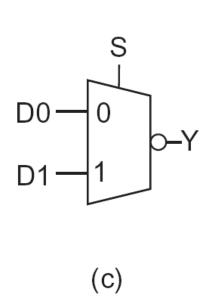

FIGURE 1.29 Inverting multiplexer

FIGURE 1.30 4:1 multiplexer

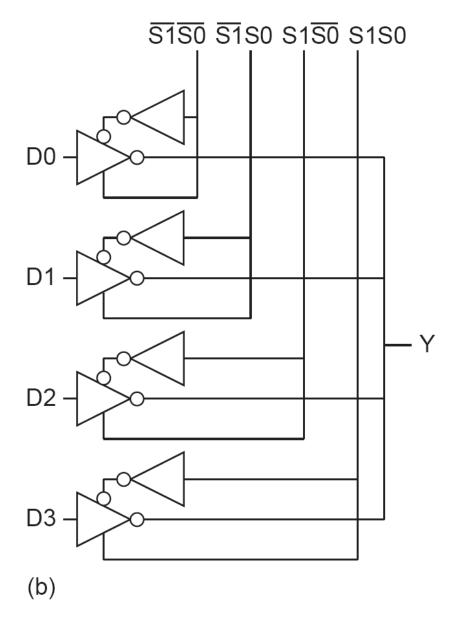

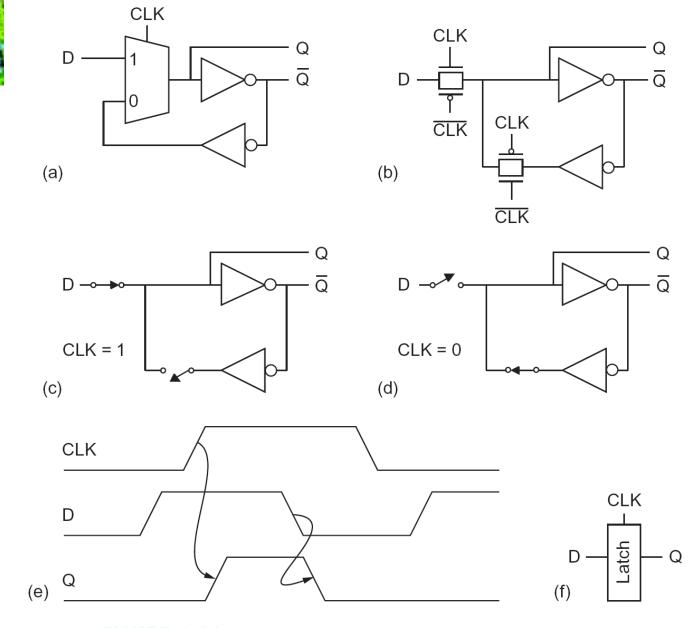

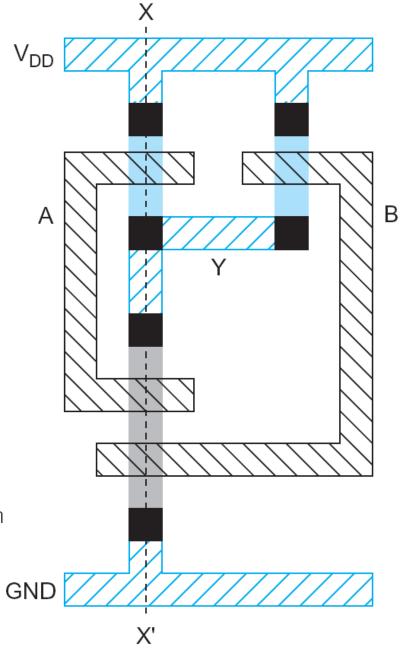

**FIGURE 1.31** CMOS positive-level-sensitive *D* latch

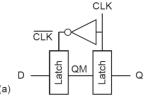

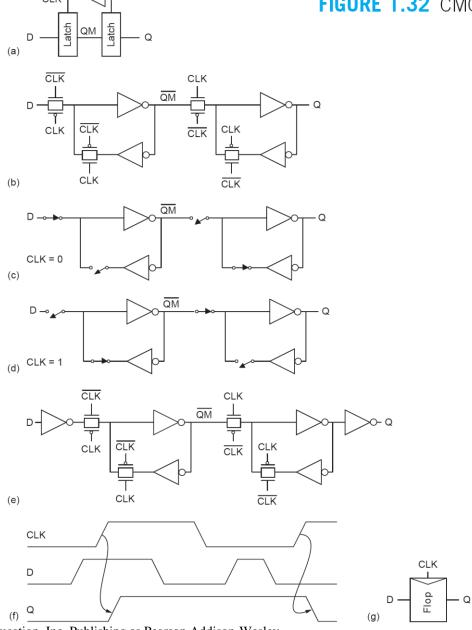

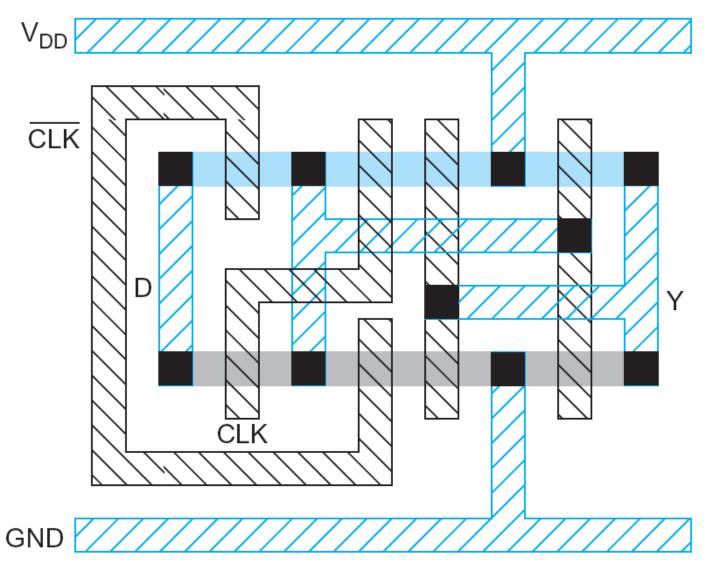

**FIGURE 1.32** CMOS positive-edge-triggered *D* flip-flop

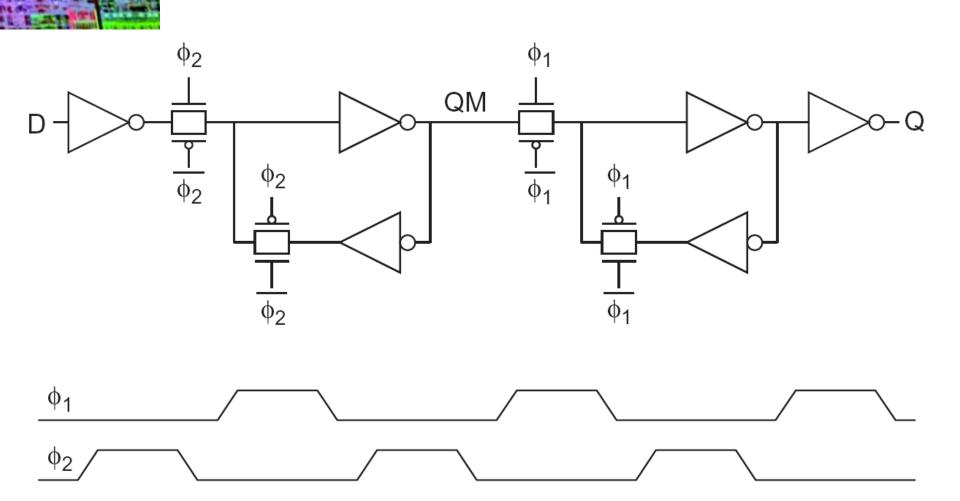

FIGURE 1.33 CMOS flip-flop with two-phase nonoverlapping clocks

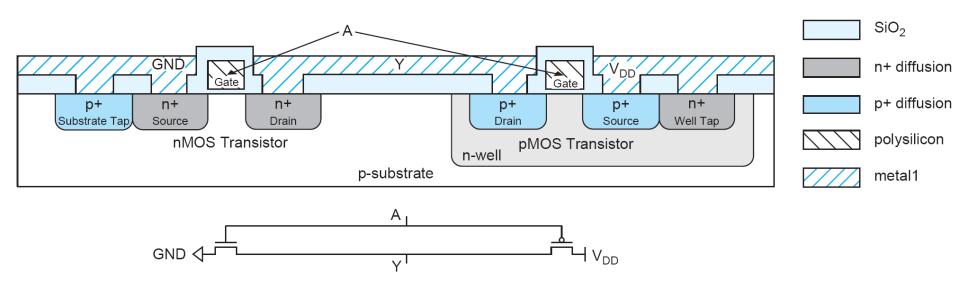

FIGURE 1.34 Inverter cross-section with well and substrate contacts. Color version on inside front cover.

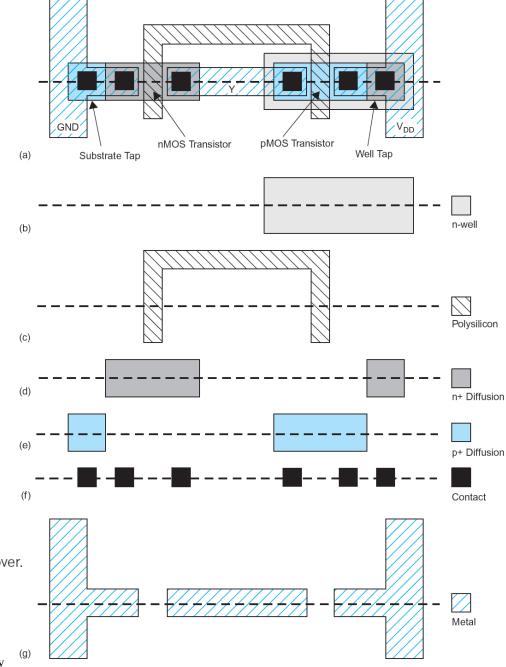

FIGURE 1.35 Inverter mask set. Color version on inside front cover.

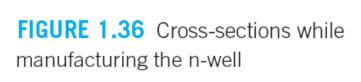

#### Polysilicon Thin gate oxide n-well p-substrate (b) n-well p-substrate (c) n-well p-substrate (d) n+ n+ n+ n-well **FIGURE 1.37** p-substrate (e) Cross-sections while manufactuing polysilicon and n-diffusion n+ n+ n+ n-well p-substrate (f)

(a)

p-substrate

Polysilicon Thin gate oxide

n-well

Copyright  $\ensuremath{\mathbb{C}}$  2011 Pearson Education, Inc. Publishing as Pearson Addison-Wesley

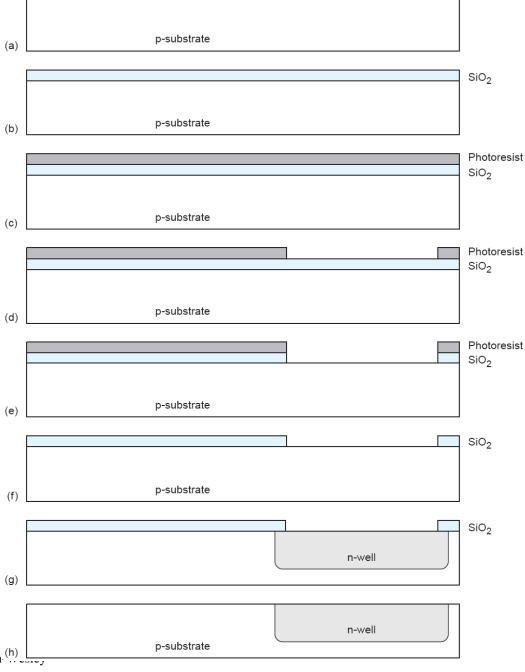

FIGURE 1.38 Cross-sections while manufacturing p-diffusion, contacts, and metal

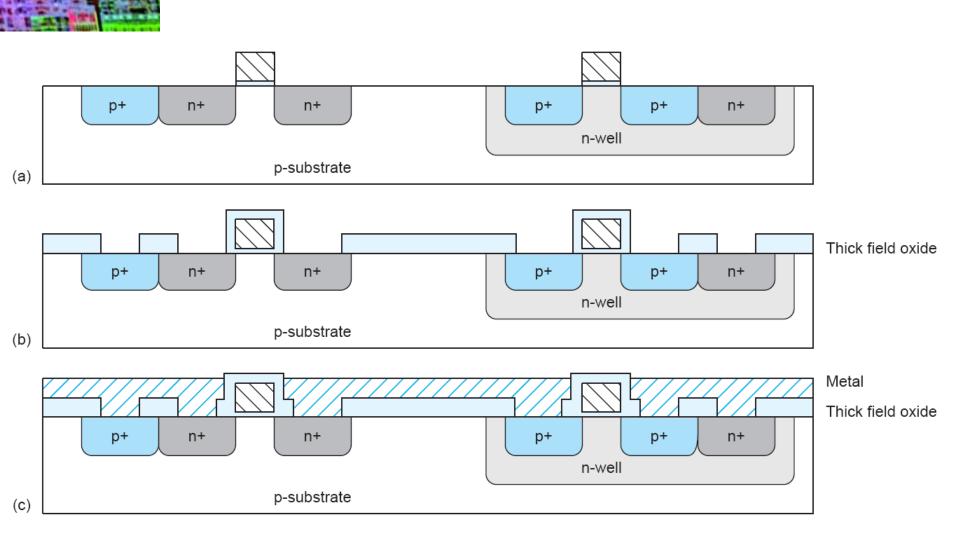

**FIGURE 1.39** Simplified  $\lambda$ -based design rules

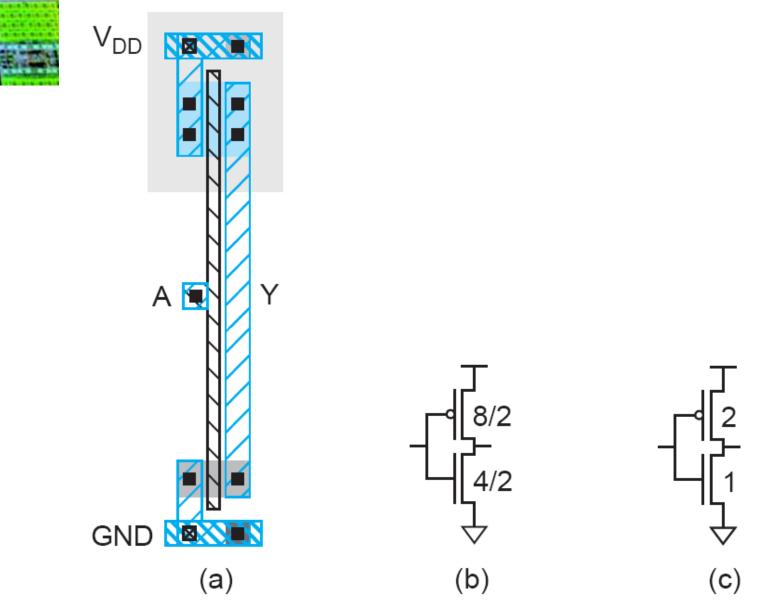

FIGURE 1.40 Inverter with dimensions labeled

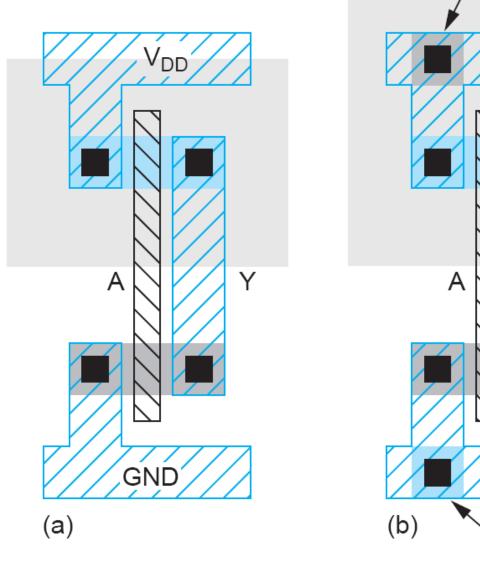

FIGURE 1.41 Inverter cell layout

Well Tap

GND

Substrate Tap

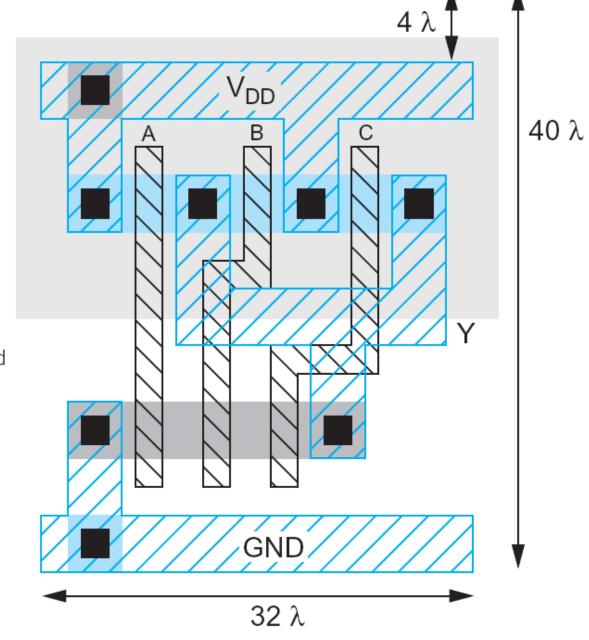

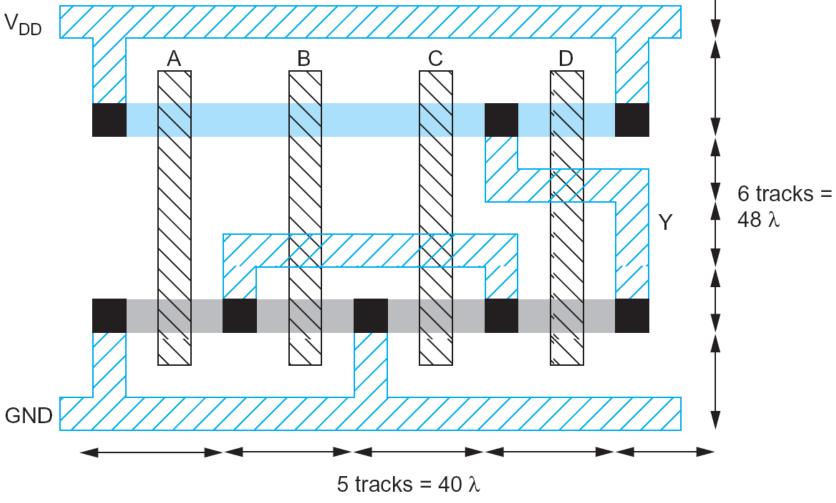

**FIGURE 1.42** 3-input NAND standard cell gate layouts

FIGURE 1.43 Stick diagrams of inverter and 3-input NAND gate. Color version on inside front cover.

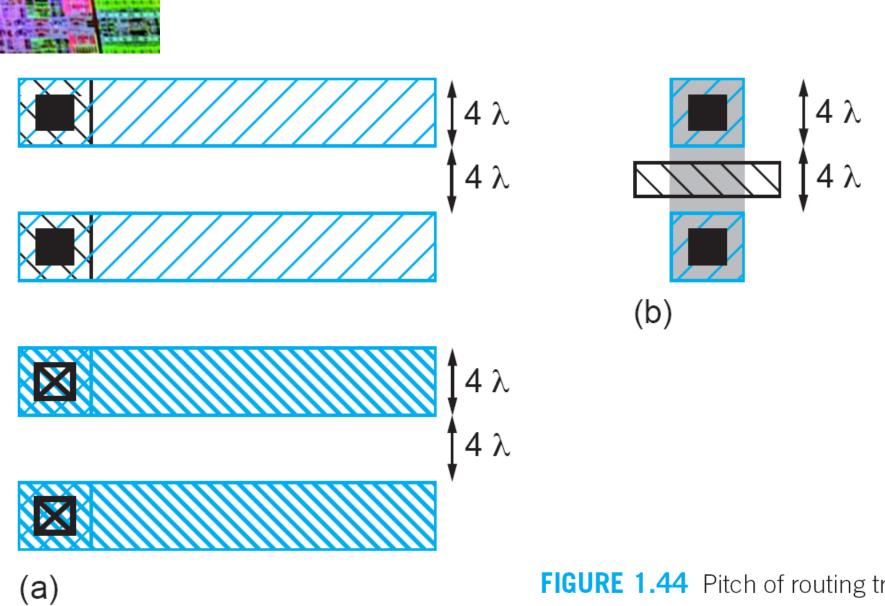

FIGURE 1.44 Pitch of routing tracks

FIGURE 1.45 Spacing between nMOS and pMOS transistors

Copyright © 2011 Pearson Education, Inc. Publishing as Pearson Addison-Wesley

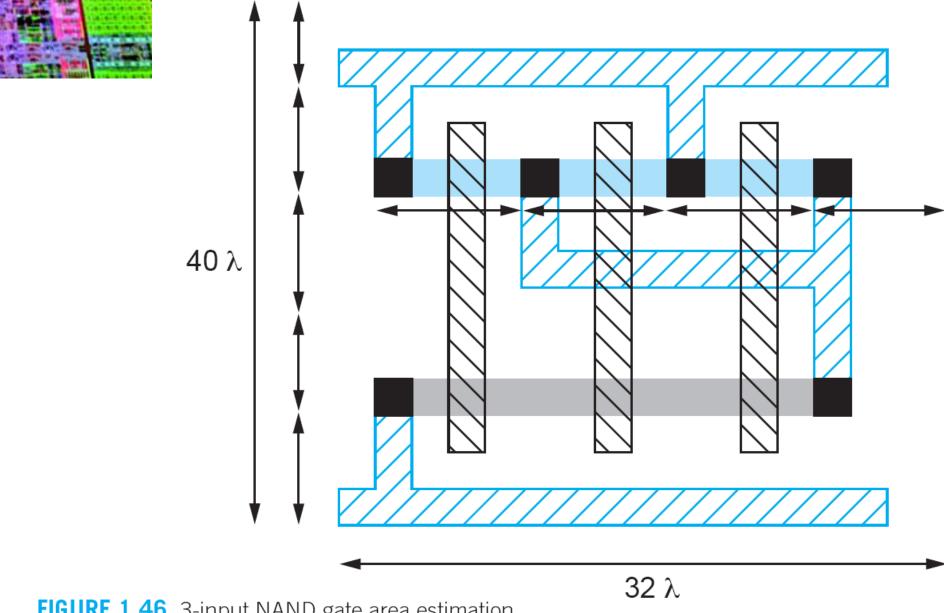

FIGURE 1.46 3-input NAND gate area estimation

**FIGURE 1.47** CMOS compound gate for function  $Y = \overline{(A + B + C) \cdot D}$

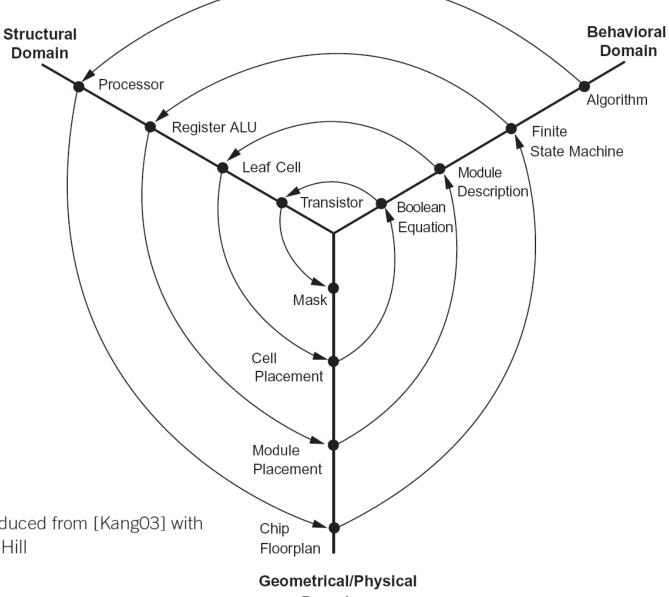

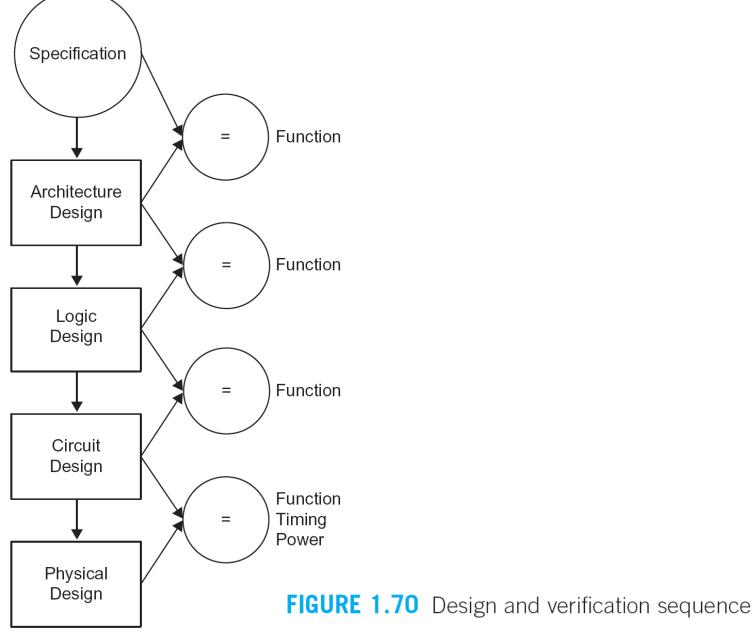

FIGURE 1.48 Y Diagram. Reproduced from [KangO3] with with permission of The McGraw-Hill Companies.

Domain

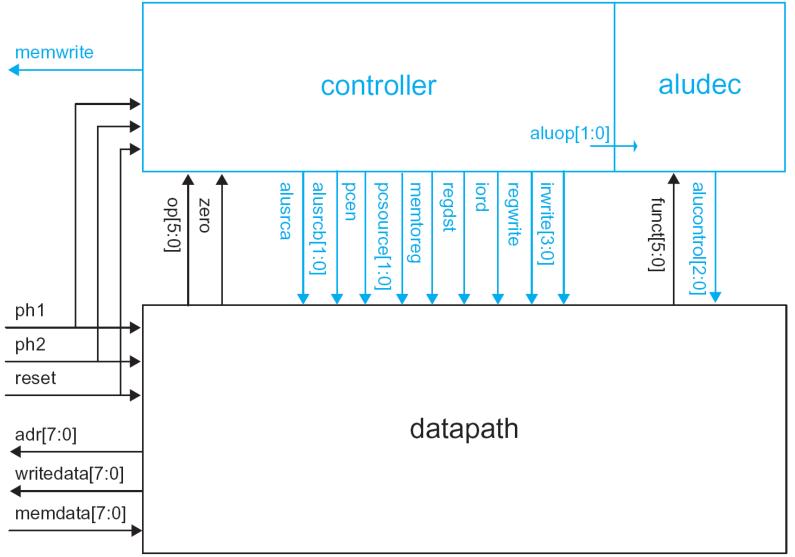

FIGURE 1.56 Top-level MIPS block diagram

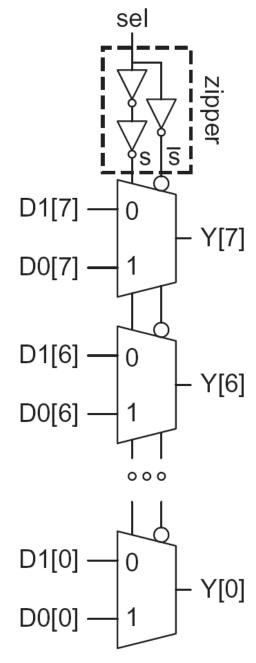

**FIGURE 1.57** 8-bit 2:1 multiplexer wordslice

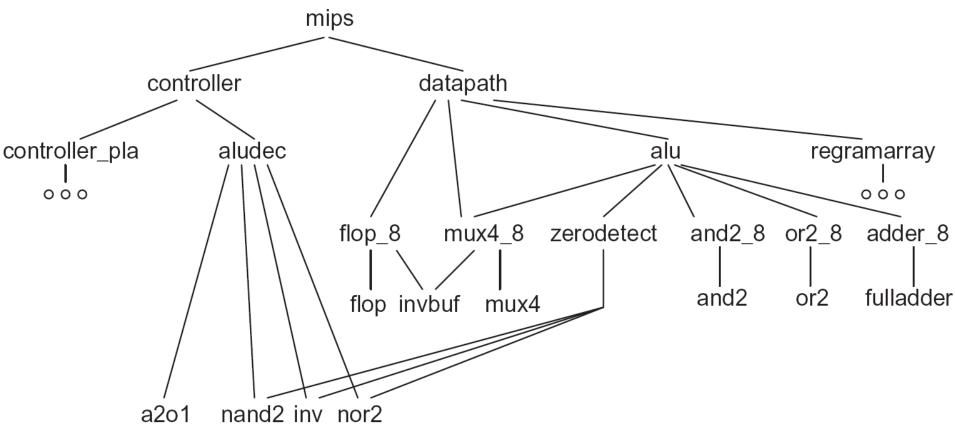

FIGURE 1.58 MIPS design hierarchy

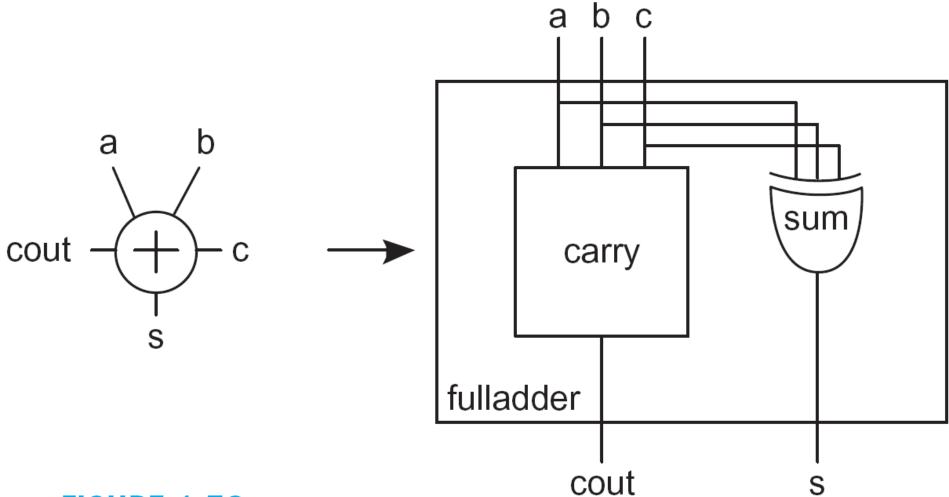

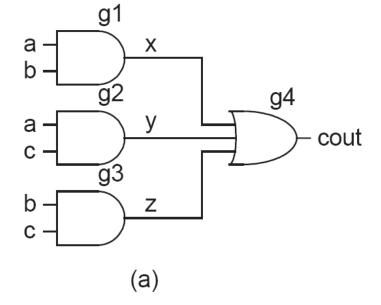

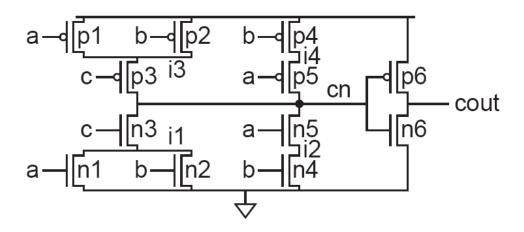

FIGURE 1.59 Full adder

FIGURE 1.60 Circuit delay and power: (a) inverter pair, (b) transistor-level model showing capacitance and current during switching, (c) static leakage current during quiescent operation

Copyright © 2011 Pearson Education, Inc. Publishing as Pearson Addison-Wesley

## FIGURE 1.61 Carry subcircuit

(b)

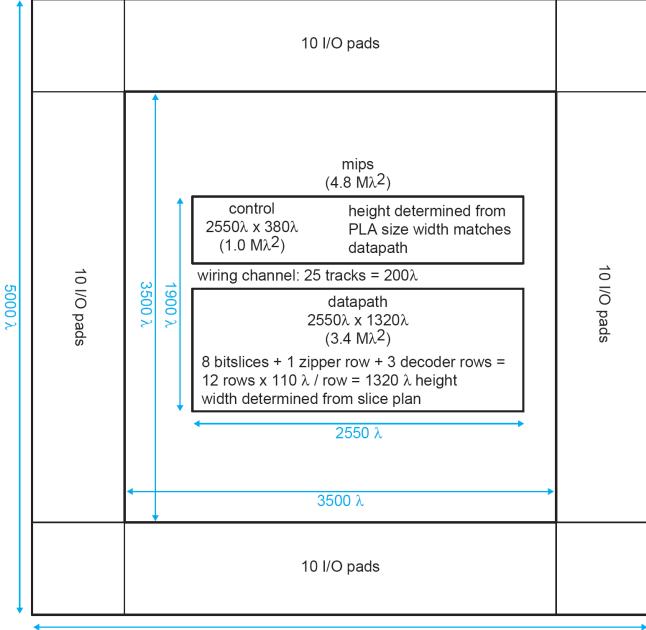

FIGURE 1.62 MIPS floorplan

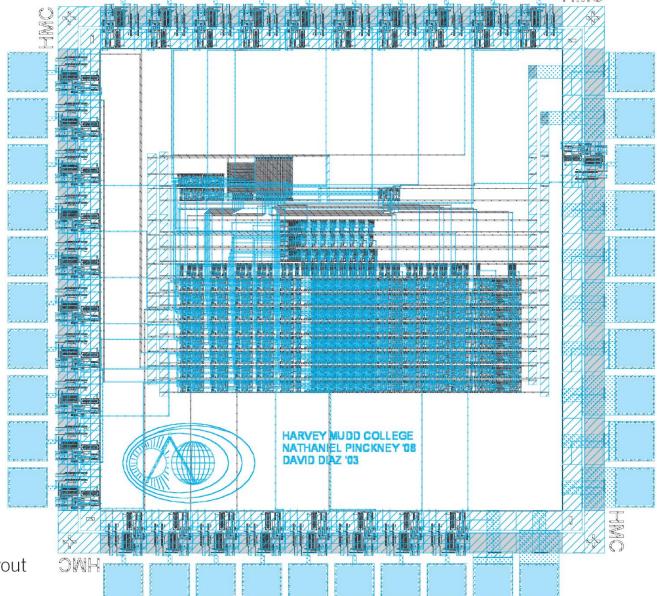

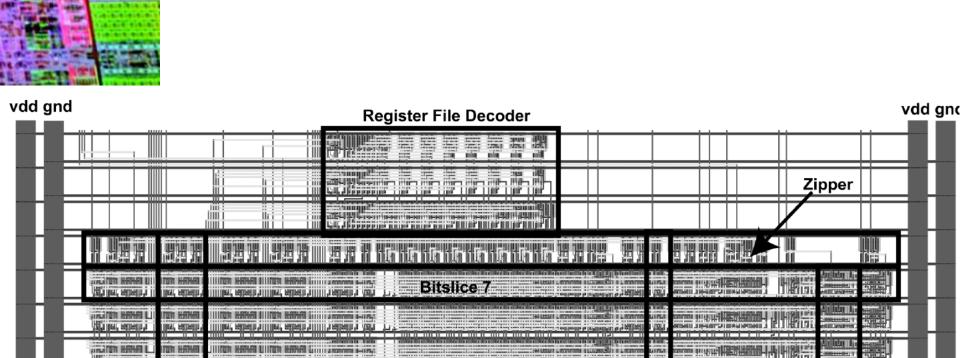

FIGURE 1.63 MIPS layout

Copyright @ 2011 Pearson Education, Inc. Publishing as Pearson Addison-Wesley

FIGURE 1.64 MIPS controller layout (synthesized)

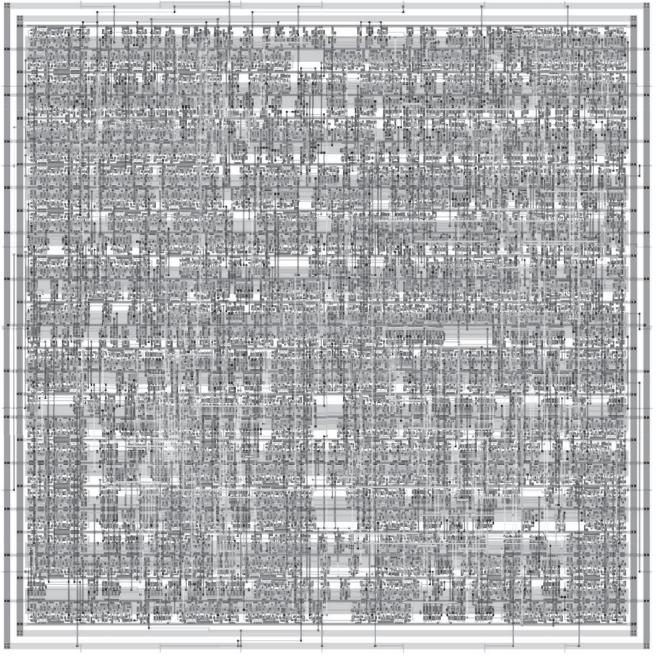

FIGURE 1.65 Synthesized MIPS processor

mux adder wordslice wordslice

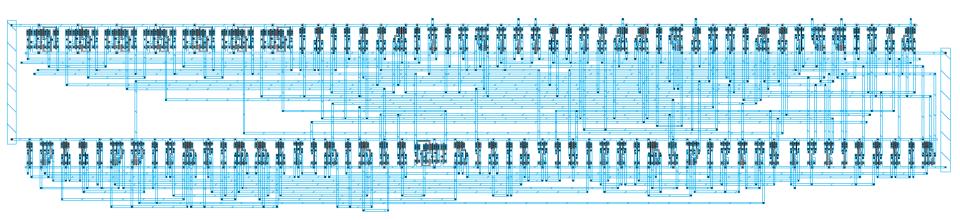

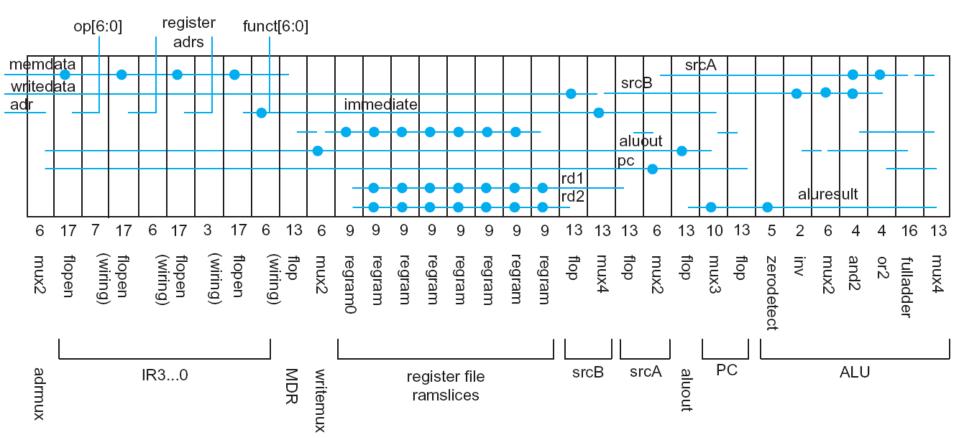

FIGURE 1.67 MIPS datapath layout

BLAT, EMITTEE

flop

wordslice

FIGURE 1.68 Datapath slice plan

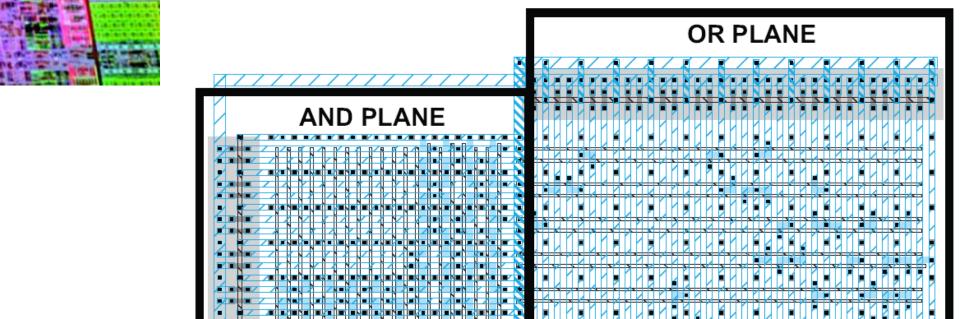

**OUTPUTS**

FIGURE 1.69 PLA for control FSM

**INPUTS**

**FIGURE 1.71** Engineer holding processed 12-inch wafer. Photograph courtesy of the Intel Corporation.

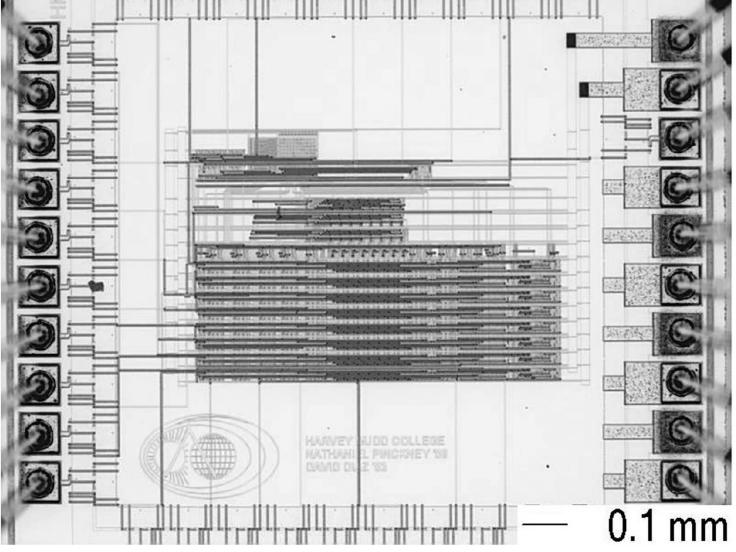

FIGURE 1.72 MIPS processor photomicrograph (only part of pad frame shown)

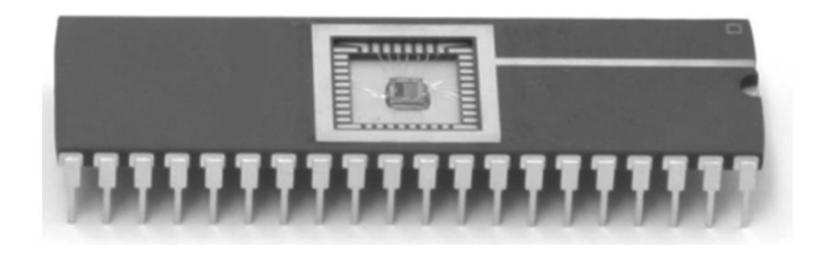

FIGURE 1.73 Chip in a 40-pin dual-inline package

FIGURE 1.74 2-input NAND gate stick diagram

FIGURE 1.75 Level-sensitive latch stick diagram